Das IEC61131-3-System Codesys wird häufig für SPS-Applikationen eingesetzt. Schließlich bietet es die Möglichkeit, den Code in verschiedene Tasks aufzuteilen und diese mit unabhängigen Zykluszeiten abzuarbeiten. Hersteller von Automatisierungsgeräten können Anwendern jetzt auch anbieten, in Codesys die verschiedenen Tasks der SPS-Applikation auf symmetrische Prozessorkerne der Steuerungs-CPU manuell zu verteilen. Durch die parallele Abarbeitung lässt sich die Ausführungsgeschwindigkeit bei gleichzeitiger Ausnutzung der verfügbaren Prozessorleistung steigern und der Anwender behält die Kontrolle über das Zeitverhalten. Steuerungen mit Betriebssystemen wie Linux oder Windows nehmen eine solche Verteilung zwar selbst vor, das daraus resultierende Zeitverhalten jedoch ist im Einzelfall schwer abzuschätzen. Zur Nutzung der umgesetzten Multicore-Implementierung ordnen Anwender im einfachsten Fall lediglich den gewünschten CPU-Kern zu Task-Gruppen der SPS-Applikation zu. Bei komplexeren Konfigurationen helfen verfügbare Codierungsrichtlinien. Gleichzeitig ist die Problematik der Datenkonsistenz bei Datenhaltung bzw. -zugriff durch entsprechende Software im Control-Laufzeitsystem gelöst.

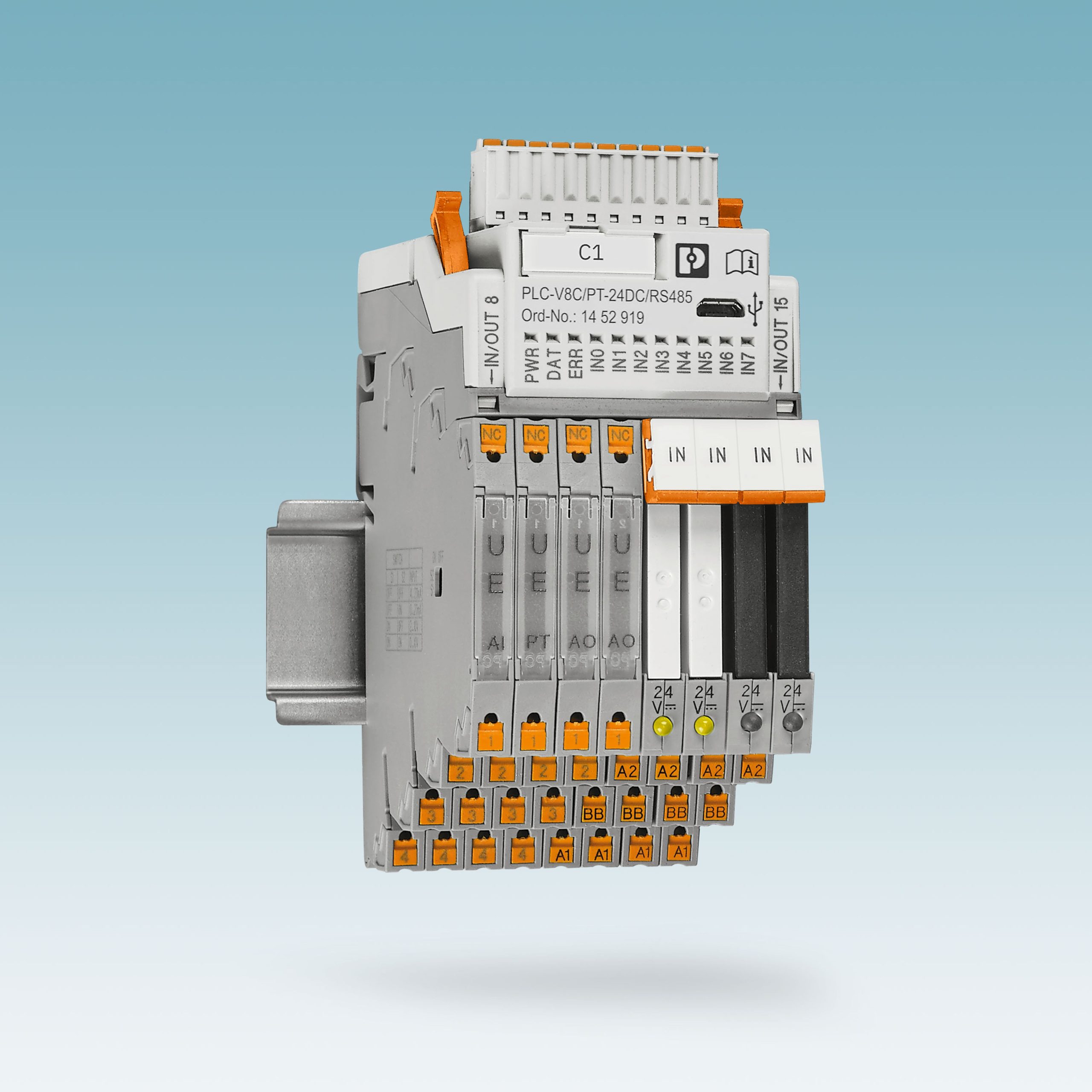

Ethercat-Analog-Klemmen in neuer Generation

Mit einer neuen Generation an Ethercat-Analog-Klemmen im kompakten HD-Gehäuse will Beckhoff die Performance der bisherigen IP20-I/Os steigern.